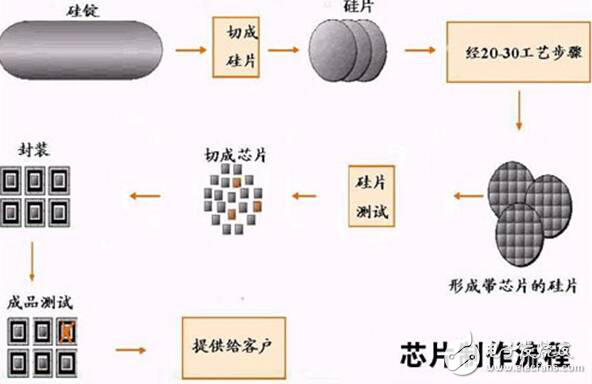

芯片不是天然长出来的,也不是宅男用电脑打印出来的。它的诞生,是个复杂漫长的旅行。简单来分,芯片制造过程有这么几个阶段:材料制备——单晶硅制造→晶圆片生成芯片前端——芯片构建(Wafer Fabrication)

芯片后端——封装(Package)→完整测试(Initial Test and Final Test)

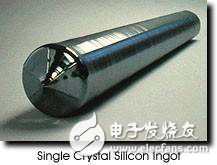

备料——硅片制作芯片的制作离不开硅,作为最主要的原料,硅的处理工作至关重要。首先,硅原料要进行化学提纯,这一步骤使其达到可供半导体工业使用的原料级别。为了使这些硅原料能够满足集成电路制造的加工需要,还必须将其整形,这一步是通过溶化硅原料,然后将液态硅注入大型高温石英容器来完成的。

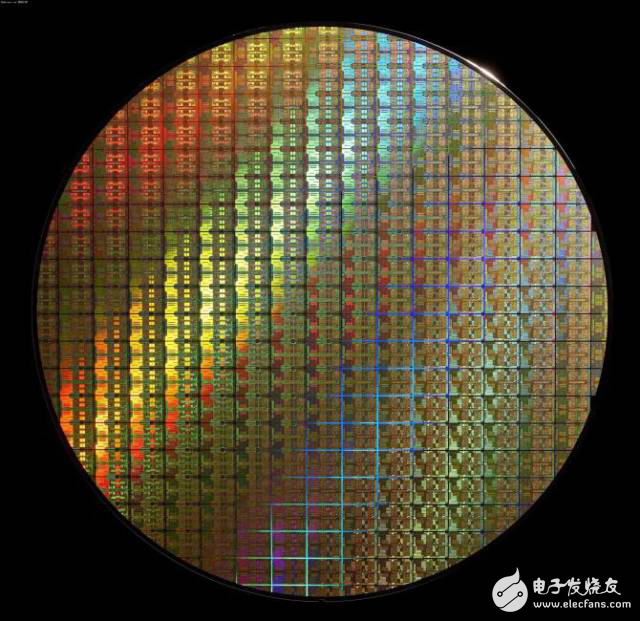

而后,将原料进行高温溶化,然后从高温容器中采用旋转拉伸的方式将硅原料取出,此时一个圆柱体的硅单晶锭就产生了。目前,业界最领先工艺生产的是300mm的硅锭,也就是12寸晶圆。

在制成硅锭并确保其是一个绝对的圆柱体之后,下一个步骤就是将这个圆柱体硅锭切片,切片越薄,用料越省,自然可以生产的处理器芯片就更多。切片还要镜面精加工的处理来确保表面绝对光滑,之后检查是否有扭曲或其它问题。这一步的质量检验尤为重要,它直接决定了成品芯片的质量。

新的切片中要掺入一些物质,使之成为真正的半导体材料,然后在其上刻划代表着各种逻辑功能的电路。掺入的物质原子进入硅原子之间的空隙,彼此之间发生原子力的作用,从而使得硅原料具有半导体的特性。今天的半导体制造多选择CMOS工艺(互补型金属氧化物半导体)。其中,互补一词表示半导体中N型MOS管和P型MOS管之间的交互作用。N和P在电子工艺中分别代表负极和正极。多数情况下,切片被掺入化学物质形成P型衬底,在其上刻划的逻辑电路要遵循nMOS电路的特性来设计,这种类型的晶体管空间利用率更高也更加节能。同时在多数情况下,必须尽量限制pMOS型晶体管的出现,因为在制造过程的后期,需要将N型材料植入P型衬底当中,这一过程会导致pMOS管的形成。

在掺入化学物质的工作完成之后,标准的切片就完成了。然后将每一个切片放入高温炉中加热,通过控制加温时间使得切片表面生成一层二氧化硅膜。通过密切监测温度,空气成分和加温时间,该二氧化硅层的厚度是可以控制的。准备工作的最后一道工序是在二氧化硅层上覆盖一个感光层。这一层物质用于同一层中的其它控制应用。这层物质在干燥时具有很好的感光效果,而且在光刻蚀过程结束之后,能够通过化学方法将其溶解并除去。光刻(Photolithography)

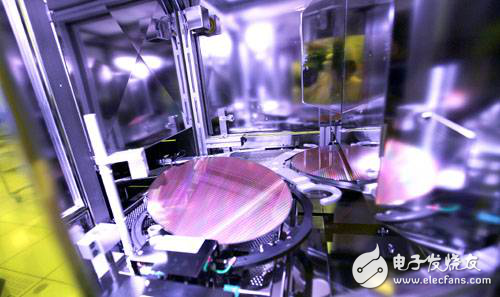

光刻是在晶圆上印制芯片电路图形的工艺,是集成电路制造的最关键步骤,在整个芯片的制造过程中约占据了整体制造成本的35%。

光刻也是决定了集成电路按照摩尔定律发展的一个重要原因,如果没有光刻技术的进步,集成电路就不可能从微米进入深亚微米再进入纳米时代。

光刻工艺将掩膜图形转移到晶片表面的光刻胶上,首先光刻胶处理设备把光刻胶旋涂到晶圆表面,再经过分步重复曝光和显影处理之后,在晶圆上形成需要的图形。

通常以一个制程所需要经过掩膜数量来表示这个制程的难易。根据曝光方式不同,光刻可分为接触式、接近式和投影式;根据光刻面数的不同,有单面对准光刻和双面对准光刻;根据光刻胶类型不同,有薄胶光刻和厚胶光刻。一般的光刻流程包括前处理、匀胶、前烘、对准曝光、显影、后烘,可以根据实际情况调整流程中的操作。

刻蚀(Etching)

在集成电路制造过程中,经过掩模套准、曝光和显影,在抗蚀剂膜上复印出所需的图形,或者用电子束直接描绘在抗蚀剂膜上产生图形,然后把此图形精确地转移到抗蚀剂下面的介质薄膜(如氧化硅、氮化硅、多晶硅)或金属薄膜上去,制造出所需的薄层图案。

刻蚀就是用化学的、物理的或同时使用化学和物理的方法,有选择地把没有被抗蚀剂掩蔽的那一部分薄膜层除去,从而在薄膜上得到和抗蚀剂膜上完全一致的图形。

等离子刻蚀(plasma etch)是在特定的条件下将反应气体电离形成等离子体,等离子体选择性地从晶圆上除去物质,剩下的物质在晶圆上形成芯片图形。 离子注入 Ion Implantation

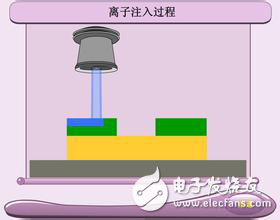

晶圆衬底是纯硅材料,不导电或导电性极弱。为了在芯片内具有导电性,必须在晶圆里掺入微量的不纯物质,通常是砷、硼、磷。掺杂可以在扩散炉中进行,也可以采用离子注入实现。一些先进的应用都是采用离子注入掺杂的。其实,最主要的目的是生成N沟道或P沟道。这个掺杂过程创建了全部的晶体管及彼此间的电路连接,没个晶体管都有输入端和输出端,两端之间被称作端口。

离子注入有中电流离子注入、大电流/低能量离子注入、高能量离子注入三种,适于不同的应用需求。

化学机械研磨

化学机械研磨(化学机器磨光,CMP)兼具有研磨性物质的机械式研磨与酸碱溶液的化学式研磨两种作用,可以使晶圆表面达到全面性的平坦化,以利后续薄膜沉积之进行。在CMP制程的硬设备中,研磨头被用来将晶圆压在研磨垫上并带动晶圆旋转,至于研磨垫则以相反的方向旋转。在进行研磨时,由研磨颗粒所构成的研浆会被置于晶圆与研磨垫间。

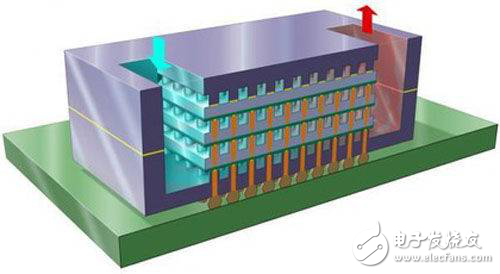

一而再再而三从这一步起,将持续添加层级,加入一个二氧化硅层,然后光刻一次。重复这些步骤,然后就出现了一个多层立体架构,这就是你目前使用的处理器的萌芽状态了。在每层之间采用金属涂膜的技术进行层间的导电连接。

这就是芯片的内部结构,看着是不是很像一座大厦。晶圆度量检测 Wafer Metrology在芯片制造过程中,为了保证晶圆按照预定的设计要求被加工必须进行大量的检测和量测,包括芯片上线宽度的测量、各层厚度的测量、各层表面形貌测量,以及各个层的一些电子性能的测量。

随着半导体工艺和制造技术的不断发展,这些检测已经成为提高量产和良率的不可缺少的部分。在铜互连工艺中,由于采用更精细的线宽技术和低k介电材料,需要开发更精密的测试设备和新的测试方法。

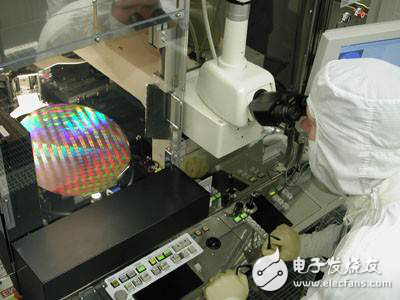

检测主要包括三类:光学检测、薄膜检测、关键尺寸扫描电子检测(CD-SEM)。晶圆检测的一个重要发展趋势是将多种测量方法融合于一个工艺设备中。

晶圆探针测试(Wafer Probe Test)这个检测是用来判别芯片好坏的。晶圆探针测试是对制造完成的晶圆上的每个芯片(Die)进行针测,测试时,晶圆被固定在真空吸力的卡盘上,并与很薄的探针电测器对准,细如毛发的探针与芯片的每一个焊接点相接触。在测试过程中,每一个芯片的电性能和电路机能都被检测到,不合格的晶粒会被标上记号,而后当芯片切割成独立的芯片颗粒时,标有记号的不合格芯片颗粒会被淘汰。探针检测的相关数据,现在已经可以用来对晶圆制造中的良率提升提供帮助。

芯片封装(Assembly & Packaging)

晶圆上的芯片在这里被切割成单个芯片,然后进行封装,这样才能使芯片最终安放在PCB板上。这里需要用的设备包括晶圆切割机,粘片机(将芯片封装到引线框架中)、线焊机(负责将芯片和引线框架的连接,如金丝焊和铜丝焊)等。在引线键合工艺中使用不同类型的引线:金(Au)、铝(Al)、铜(Cu),每一种材料都有其优点和缺点,通过不同的方法来键合。随着多层封装乃至3D封装的应用的出现,超薄晶圆的需求也在不断增强。芯片做好了,到了电工手里,经过熟练地焊接工艺,镶嵌在PCB上,最终变成了电子产品的心脏。

评 论

请勿进行人身攻击,谩骂以及任何违法国家相关法律法规的言论。

正在加载评论...